IT管理與計算機軟件開發 協同共進的技術雙輪

在當今數字化浪潮席卷全球的背景下,IT管理與計算機軟件開發已成為推動企業創新與效率提升的核心驅動力。兩者雖職責不同,卻如同鳥之雙翼、車之雙輪,緊密關聯,協同共進,共同構建了現代企業穩健、敏捷的技術生態體系。

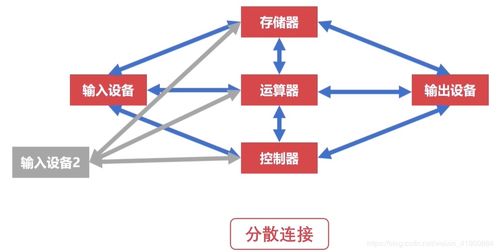

IT管理,其核心在于規劃、組織、實施與維護企業的信息技術資源與系統。它涵蓋了從基礎設施(如服務器、網絡)的運維,到信息系統安全、數據治理、服務支持乃至IT戰略與企業業務目標的戰略對齊。一個優秀的IT管理體系能夠確保技術環境的穩定性、安全性與成本效益,為企業的日常運營與長遠發展提供堅實可靠的“數字底座”。其價值在于將技術從單純的工具提升為戰略資產,通過流程化、標準化的管理,最大化技術投資回報,并有效管控風險。

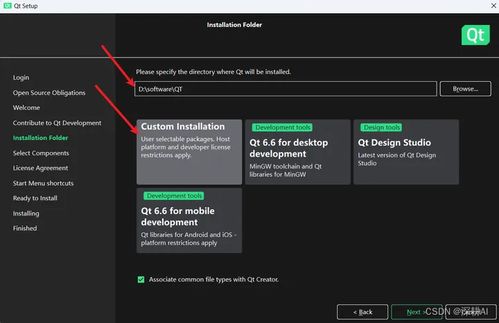

計算機軟件開發,則是這一“數字底座”上持續創造價值的引擎。它聚焦于通過設計、編碼、測試和維護等一系列工程化活動,構建滿足特定業務需求或解決實際問題的軟件應用。從桌面軟件到移動應用,從企業級ERP系統到前沿的人工智能算法,軟件開發是將創新想法轉化為具體功能與用戶體驗的關鍵過程。敏捷開發、DevOps等現代方法論的應用,極大地提升了軟件交付的速度與質量,使企業能夠快速響應市場變化。

兩者的關系并非簡單的“管理”與“被管理”。在理想狀態下,它們是深度融合、相互賦能的:

- 戰略協同:IT管理為軟件開發設定框架與邊界。IT戰略規劃定義了技術棧選擇、架構標準和安全合規要求,確保軟件開發活動與企業整體技術路線圖保持一致,避免形成“信息孤島”和技術債務。軟件開發中涌現的新需求與技術趨勢(如云原生、微服務),也會反過來推動IT管理策略與基礎設施的演進與升級。

- 流程與效率:現代IT管理實踐,特別是DevOps文化和平臺工程,旨在打通開發與運維的壁壘。通過自動化工具鏈(CI/CD)、統一監控和敏捷的運維響應,IT管理為軟件開發團隊提供了自助服務能力和高效的部署環境,顯著縮短了從代碼提交到功能上線的周期,實現了業務的快速迭代與創新。

- 質量與安全左移:IT管理中的安全策略(如SecOps)和質量保障要求,正日益深入地嵌入到軟件開發生命周期(SDLC)的早期階段。這意味著開發人員在設計、編碼時就需要考慮安全性、可維護性和性能,而非在最后階段進行補救。這種“左移”理念通過管理流程的介入,從源頭提升了軟件產品的內在質量與韌性。

- 資源優化與價值衡量:IT管理通過對計算資源、許可證和項目投資的精細化管理,確保軟件開發活動在成本可控的范圍內高效進行。通過建立價值流指標,IT管理可以幫助衡量軟件開發所創造的實際業務價值,使技術投入與產出清晰可見。

挑戰依然存在。技術迭代的加速、安全威脅的復雜化、以及對跨領域復合型人才的需求,都要求IT管理與軟件開發必須保持更緊密的對話與合作。未來的趨勢將是進一步的融合——IT管理者需要深刻理解開發流程與技術細節,以提供更具賦能性的平臺與服務;軟件開發者也需具備更強的系統思維、安全意識與成本意識,在創造的同時考慮到整個生命周期的可管理性。

卓越的IT管理為計算機軟件開發提供了穩定、安全、高效的舞臺與規則,而充滿活力的軟件開發則不斷拓展這個舞臺的邊界,為企業注入持續的創新活力。二者相輔相成,共同驅動著企業在數字經濟時代的轉型與成功。只有將管理的秩序與開發的創造力有機結合,組織才能在技術驅動的競爭中立于不敗之地。

如若轉載,請注明出處:http://www.xtlnx.cn/product/48.html

更新時間:2026-04-12 13:24:24