軟件開發視角下的計算機組成原理 核心組成篇

在軟件開發的世界里,代碼是思想的載體,程序是邏輯的具現。所有精妙的算法與優雅的架構,最終都需要依賴其物理基石——計算機硬件系統來執行。理解計算機的組成原理,對于軟件開發人員而言,絕非紙上談兵的理論課,而是通往編寫高效、穩健、深刻理解系統行為的代碼的必經之路。本文將從軟件開發者的實用視角,重新審視計算機的核心組成部件及其深遠影響。

1. 中央處理器(CPU):指令的執行引擎與編程思維的映射

CPU是計算機的“大腦”,也是軟件指令的最終執行者。對于開發者而言,理解CPU的運算器、控制器、寄存器組以及時鐘頻率,直接影響著我們對程序性能的認知。

- 寄存器與高速緩存:它們是CPU的“工作臺”和“臨時倉庫”。理解寄存器的存在(如通用寄存器、指令指針)有助于我們明白變量操作的底層速度差異。高速緩存(L1/L2/L3)的層次結構,則直接解釋了為何局部性原理(時間局部性與空間局部性)對程序性能至關重要。編寫緩存友好的代碼,能極大提升數據處理效率。

- 指令集架構(ISA):這是軟件與硬件之間的關鍵契約。無論是x86、ARM還是RISC-V,ISA定義了CPU能理解的基本操作(指令)。高級語言編譯后的機器碼,正是由這些指令序列構成。了解ISA有助于我們進行底層優化、理解編譯器行為,甚至在嵌入式開發或性能調優時進行內聯匯編。

- 多核與并行:現代CPU的多核結構催生了并發與并行編程。理解核心、線程(超線程技術)之間的資源共享與競爭,是編寫正確、高效多線程程序(如使用Java的Concurrent包、C++的STL多線程庫)的基礎。緩存一致性協議(如MESI)引發的“偽共享”問題,就是硬件組成直接影響軟件設計的典型例證。

2. 存儲器系統:數據的層級王國與程序的生命周期

從寄存器的納秒級訪問到硬盤的毫秒級尋道,存儲器系統是一個巨大的速度與容量權衡的階梯。軟件開發者必須對此有清晰的認識。

- 內存(RAM):這是程序運行時的主戰場。操作系統將進程的代碼、數據、堆棧段加載于此。理解內存的隨機訪問特性與物理/虛擬內存機制,關乎到:

- 內存管理:在C/C++等語言中手動管理堆內存,必須警惕內存泄漏與野指針。

- 數據結構布局:數組的連續存儲帶來高速緩存優勢,而鏈表的指針跳轉則可能引發緩存失效。

- 虛擬內存與分頁:這允許我們使用遠大于物理內存的地址空間。“缺頁中斷”是影響程序性能的一個潛在因素,特別是在處理大數據集時。

- 外存(硬盤/SSD):作為持久化存儲,這里是數據庫、文件系統以及所有需要長期保存數據的歸宿。I/O操作是程序的常見瓶頸。理解磁盤的尋道時間、旋轉延遲與固態硬盤(SSD)的并行訪問特性,對于設計數據庫索引、優化文件讀寫流程至關重要。例如,順序訪問遠快于隨機訪問,這一硬件特性直接影響了日志結構合并樹(LSM-Tree)等存儲引擎的設計。

- 存儲層次結構的意義:軟件設計的許多模式,實質上是這一硬件層次結構的映照。例如,CPU緩存 -> 內存 -> 磁盤的層次,對應著程序中的“緩存”(如Redis)-> 數據庫 -> 冷備份歸檔的數據生命周期管理策略。

3. 輸入輸出(I/O)系統:與世界的接口和異步編程之源

I/O系統是計算機與外部世界(用戶、網絡、其他設備)交互的渠道。對于開發網絡服務、圖形界面或驅動程序的軟件來說,這里是核心關注點。

- I/O控制方式:從程序輪詢(Polling)到中斷(Interrupt)再到直接內存訪問(DMA),硬件的進步不斷將CPU從繁重的I/O等待中解放出來。這直接對應著軟件編程模型的演進:

- 同步阻塞I/O:模擬了最簡單的輪詢/等待,編程簡單但效率低下。

- 多線程/多進程:利用并發來掩蓋I/O阻塞時間。

- 異步I/O與事件驅動:這是對中斷和DMA機制的更高層抽象。如Node.js的異步非阻塞、Nginx的事件驅動模型,其高效性正是基于硬件I/O能力的充分發揮。操作系統提供的select/poll/epoll(Linux)或IOCP(Windows)等系統調用,是這一硬件-軟件協同的關鍵接口。

- 總線與接口:了解PCIe、USB、SATA等總線協議的標準與帶寬,有助于在系統集成、驅動開發或高性能計算(如GPU通過PCIe與CPU通信)時做出合理設計。

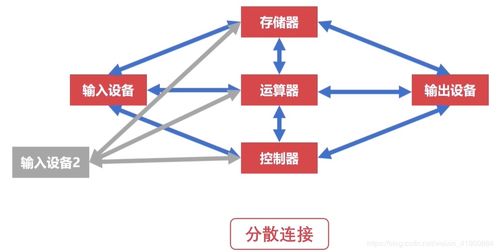

4. 系統總線:數據流動的“高速公路”與并發之踵

總線是連接CPU、內存、I/O設備的公共通信干線。它的寬度(位寬)、時鐘頻率和仲裁協議,決定了數據在組件間流動的峰值帶寬。對于軟件開發者,尤其是從事高性能計算、游戲引擎或底層系統編程的人員,總線帶寬可能成為性能瓶頸。在多處理器系統中,總線仲裁和一致性協議更是保證了多核協同工作的正確性,這也是我們在編寫并發程序時需要依賴的內存模型(如Java的Happens-Before規則、C++的內存序)的硬件基礎。

從抽象回歸具體,賦能軟件開發

深入理解計算機的組成——CPU、存儲器、I/O系統和總線,并非要求每位開發者都去設計硬件。其價值在于:

- 寫出更高效的代碼:知道硬件如何工作,就能避免寫出讓硬件“難受”的代碼,例如不必要的內存隨機訪問、緩存不友好的數據結構。

- 進行更精準的性能調優:當程序出現性能問題時,能夠結合CPU緩存命中率、內存帶寬、I/O等待時間等硬件指標進行剖析,而非盲目猜測。

- 理解高級抽象的底層代價:虛擬機、容器、垃圾回收、協程……這些高級軟件抽象背后,都有其硬件成本和優化邏輯。理解組成原理,能讓我們更明智地使用這些工具。

- 拓寬技術視野與解決問題的能力:從晶體管到高級語言,計算機組成原理是貫穿其中的主線。掌握它,意味著你能在軟件與硬件的交界處游刃有余,無論是優化一個關鍵算法,還是診斷一個復雜的生產環境性能問題。

因此,將“計算機組成原理”視為軟件開發者的必修內功而非選修理論,主動將芯片、內存條、總線與我們所寫的每一行代碼聯系起來,我們便能真正地“搞定”系統,創造出不僅功能正確,而且性能卓越、資源利用率高的優秀軟件。

如若轉載,請注明出處:http://www.xtlnx.cn/product/60.html

更新時間:2026-04-12 02:31:50